3501 ED BLUESTEIN BLVD., AUSTIN, TEXAS 78721

# MC6801 MC6803

#### MICROCOMPUTER/MICROPROCESSOR (MCU/MPU)

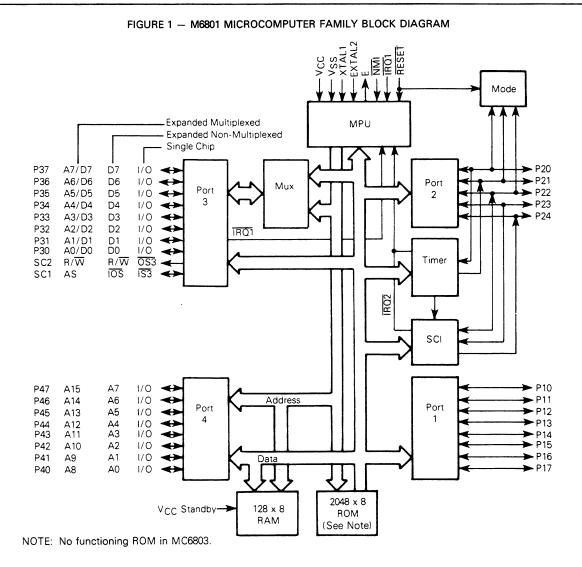

The MC6801 is an 8-bit single-chip microcomputer unit (MCU) which significantly enhances the capabilities of the M6800 Family of parts. It includes an upgraded M6800 microprocessor unit (MPU) with upwardsource and object-code compatibility. Execution times of key instructions have been improved and several new instructions have been added including an unsigned multiply. The MCU can function as a monolithic microcomputer or can be expanded to a 64K byte address space. It is TTL compatible and requires one +5-volt power supply. Onchip resources include 2048 bytes of ROM, 128 bytes of RAM, a serial communications interface (SCI), parallel I/O, and a three-function programmable timer. The MC6803 can be considered as an MC6801 operating in modes 2 or 3. An EPROM version of the MC6801, the MC68701 microcomputer, is available for systems development. The MC68701 is pin and code compatible with the MC6801/03 and can be used to emulate the MC6801/03. The MC68701 is described in a separate Advance Information publication.

- Enhanced MC6800 Instruction Set

- 8×8 Multiply Instruction

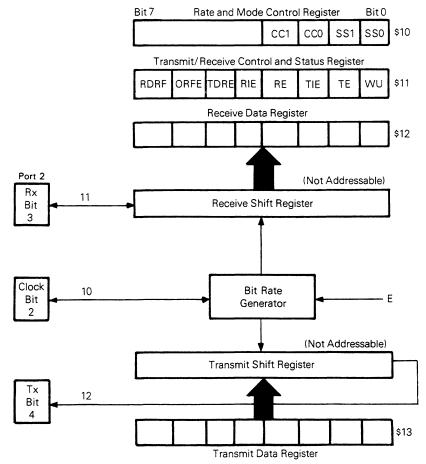

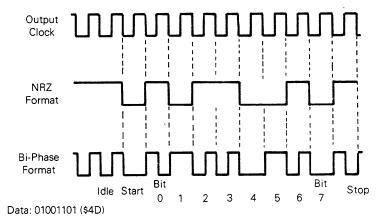

- Serial Communications Interface (SCI)

- Upward Source and Object Code Compatibility with the M6800

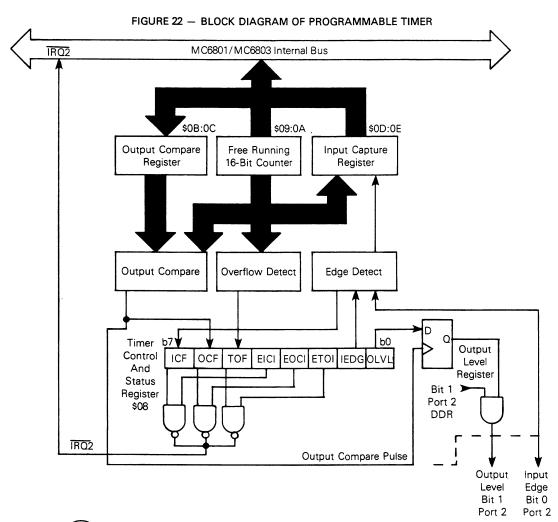

- 16-Bit Three-Function Programmable Timer

- Single-Chip or Expanded Operation to 64K Byte Address Space

- Bus Compatibility with the M6800 Family

- 2048 Bytes of ROM (MC6801 Only)

- 128 Bytes of RAM

- 64 Bytes of RAM Retainable During Powerdown

- 29 Parallel I/O and Two Handshake Control Lines

- Internal Clock Generator with Divide-by-Four Output

- −40 to 85°C Temperature Range

- − 40 to 105°C Temperature Range

#### **GENERIC INFORMATION**

|                           |                 | Generic Number              |                             |  |  |  |  |

|---------------------------|-----------------|-----------------------------|-----------------------------|--|--|--|--|

| Frequency MHz Temperature |                 | Ceramic Package<br>L Suffix | Plastic Package<br>P Suffix |  |  |  |  |

| 1.0                       | 0°C to 70°C     | MC6801L1                    | MC6801P1                    |  |  |  |  |

| 1.0                       | -40°C to 85°C   | MC6801CL1                   | MC6801CP1                   |  |  |  |  |

| 1.0                       | - 40°C to 105°C | MC6801VL1                   | MC6801VP1                   |  |  |  |  |

| 1.0                       | 0°C to 70°C     | MC6803L                     | MC6803P                     |  |  |  |  |

| 1.0                       | -40°C to 85°C   | MC6803CL                    | MC6803CP                    |  |  |  |  |

| 1.0                       | - 40°C to 105°C | MC6803VL                    | MC6803VP                    |  |  |  |  |

| 1.25                      | 0°C to 70°C     | MC6801L1-1                  | MC6803P1-1                  |  |  |  |  |

| 1.25                      | -40°C to 85°C   | MC6801CL1-1                 | MC6803CP1-1                 |  |  |  |  |

| 1.25                      | 0°C to 70°C     | MC6803L1                    | MC6803P1                    |  |  |  |  |

| 1.25                      | -40°C to 85°C   | MC6803CL-1                  | MC6803CP-1                  |  |  |  |  |

| 1.5                       | 0°C to 70°C     | MC68A01L1                   | MC68A01P1                   |  |  |  |  |

| 1.5                       | 0°C to 70°C     | MC68A03L                    | MC68A03P                    |  |  |  |  |

| 2.0                       | 0°C to 70°C     | MC68B01L1                   | MC68B01P1                   |  |  |  |  |

| 2.0                       | 0°C to 70°C     | MC68B03L                    | MC68B03P                    |  |  |  |  |

#### MOS

(N-CHANNEL, SILICON-GATE, DEPLETION LOAD)

MICROCOMPUTER MICROPROCESSOR

#### PIN ASSIGNMENT 40 **1** E V<sub>SS</sub> II 1 XTAL1 2 39 1 SC1 38 **1** SC2 EXTAL2 13 37 P30 NMI d 4 36 P31 **TRQ1** 5 RESET **1**6 35 T P32 34 D P33 Vcc 17 P20 **1** 8 33 D P34 32 1 P35 P21 **1** 9 31 D P36 P22 110 P23 🚺 11 30 T P37 29 T P40 P24 **1**12 28 P41 P10 113 P11 114 27 P42 P12 15 26 P43 25 P44 P13 16 24 D P45 P14 117 P15 118 23 🗖 P46 22 P47 P16 119 21 UCC Standby

#### **POWER CONSIDERATIONS**

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \bullet \theta_{JA}) \tag{1}$$

Where:

$T_A \equiv Ambient Temperature, °C$

$\theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient, °C/W

$P_D = P_{INT} + P_{PORT}$

PINT≡ICC×VCC, Watts - Chip Internal Power

PPORT = Port Power Dissipation, Watts - User Determined

For most applications PPORT≪PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$$P_D = K \div (T_J + 273^{\circ}C)$$

(2)

Solving equations 1 and 2 for K gives:

$$K = P_{D} \bullet (T_A + 273 \circ C) + \theta_{JA} \bullet P_{D}^2$$

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K the values of  $P_D$  and  $T_J$  can be obtained by solving equations (1) and (2) iteratively for any value of  $T_A$ .

#### **MAXIMUM RATINGS**

| Rating                                                                                | Symbol           | Value                                                                    | Unit |

|---------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------|------|

| Supply Voltage                                                                        | Vcc              | -0.3  to  +7.0                                                           | V    |

| Input Voltage                                                                         | V <sub>in</sub>  | -0.3  to  +7.0                                                           | V    |

| Operating Temperature Range<br>MC6801, MC6803<br>MC6801C, MC6803C<br>MC6801V, MC6803V | ТД               | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>– 40 to 85<br>– 40 to 105 | °C   |

| Storage Temperature Range                                                             | T <sub>stg</sub> | -55 to + 150                                                             | °C   |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation it is recommended that  $V_{in}$  and  $V_{out}$  be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{CC}$ . Input protection is enhanced by connecting unused inputs to either  $V_{DD}$  or  $V_{SS}$ .

#### THERMAL CHARACTERISTICS

| Characteristic     | Symbol        | Value | Rating |

|--------------------|---------------|-------|--------|

| Thermal Resistance |               |       |        |

| Plastic            | $\theta_{JA}$ | 50    | °C/W   |

| Ceramic            |               | 50    |        |

#### **CONTROL TIMING** ( $V_{CC} = 5.0 \text{ V } \pm 5\%$ , $V_{SS} = 0$ , $T_{A} = 0$ to $70^{\circ}\text{C}$ )

|                                  |                 | MC6801 |     | MC6801-1 |      | MC68A01 |          | MC68B01 |     | 11-14 |

|----------------------------------|-----------------|--------|-----|----------|------|---------|----------|---------|-----|-------|

| Characteristic                   | Symbol          | Min    | Max | Min      | Max  | Min     | Max      | Min     | Max | Unit  |

| Frequency of Operation           | fo              | 0.5    | 1.0 | 0.5      | 1.25 | 0.5     | 1.5      | 0.5     | 2.0 | MHz   |

| Crystal Frequency                | fXTAL           | 2.0    | 4.0 | 2.0      | 5.0  | 2.0     | 6.0      | 2.0     | 8.0 | MHz   |

| External Oscillator Frequency    | 4f <sub>O</sub> | 2.0    | 4.0 | 2.0      | 5.0  | 2.0     | 6.0      | 2.0     | 8.0 | MHz   |

| Crystal Oscillator Start Up Time | trc             | _      | 100 | _        | 100  | _       | 100      | _       | 100 | ms    |

| Processor Control Setup Time     | tPCS            | 200    | _   | 170      | _    | 140     | <b>-</b> | 110     | T - | ns    |

#### DC ELECTRICAL CHARACTERISTICS ( $V_{CC} = 5.0 \text{ Vdc} \pm 5\%$ , $V_{SS} = 0$ , $T_A = T_1$ to $T_H$ , unless otherwise noted)

|                                                                                                   |                                     |                                     |                                              | MC6801<br>MC6803     |                                              | 801C<br>803C          | MC68                                         |                      |      |

|---------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|----------------------------------------------|----------------------|----------------------------------------------|-----------------------|----------------------------------------------|----------------------|------|

| Characteristic                                                                                    |                                     | Symbol                              | Min                                          | Max                  | Min                                          | Max                   | Min                                          | Max                  | Unit |

| Input High Voltage                                                                                | RESET                               |                                     | V <sub>SS</sub> + 4.0                        |                      | V <sub>SS</sub> +4.0                         |                       | V <sub>SS</sub> +4.0                         |                      |      |

|                                                                                                   | Other Inputs                        | VIH                                 | $V_{SS} + 2.0$                               |                      | $V_{SS} + 2.2$                               |                       | $V_{SS} + 2.2$                               |                      | V    |

| Input Low Voltage                                                                                 | All Inputs                          | VIL                                 | $V_{SS} - 0.3$                               | V <sub>SS</sub> +0.8 | V <sub>SS</sub> -0.3                         | V <sub>SS</sub> + 0.8 | V <sub>SS</sub> -0.3                         | $V_{SS} + 0.7$       | V    |

| Input Load Current                                                                                | Port 4                              |                                     | -                                            | 0.5                  | _                                            | 0.8                   | -                                            | 0.8                  |      |

| $(V_{in} = 0 \text{ to } 2.4 \text{ V})$                                                          | SCI_                                | l <sub>in</sub>                     | _                                            | 0.8                  | -                                            | 1.0                   | _                                            | 1.0                  | mΑ   |

| Input Leakage Current (V <sub>in</sub> = 0 to 5.25 V)                                             | NMI, IRQ1, RESET                    | l <sub>in</sub>                     | _                                            | 2.5                  | _                                            | 5.0                   | _                                            | 5.0                  | μΑ   |

| Hi-Z (Off State) Input Current (V <sub>in</sub> = 0.5 to 2.4 V)                                   | Ports 1, 2, and 3                   | <sup> </sup> TSI                    | _                                            | 10                   | _                                            | 20                    | _                                            | 20                   | μΑ   |

| Output High Voltage $(I_{Load} = -65 \mu A, V_{CC} = Min)* (I_{Load} = -100 \mu A, V_{CC} = Min)$ | Port 4, SC1, SC2<br>Other Outputs   |                                     | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4 |                      | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4 |                       | V <sub>SS</sub> +2.4<br>V <sub>SS</sub> +2.4 |                      | ٧    |

| Output Low Voltage (I <sub>Load</sub> = 2.0 mA, V <sub>CC</sub> = Min)                            | All Outputs                         | Vol                                 | _                                            | V <sub>SS</sub> +0.5 | _                                            | V <sub>SS</sub> +0.6  | _                                            | V <sub>SS</sub> +0.6 | V    |

| Darlington Drive Current (V <sub>O</sub> = 1.5 V)                                                 | Port 1                              | ІОН                                 | 1.0                                          | 4.0                  | 1.0                                          | 5.0                   | 1.0                                          | 5.0                  | mA   |

| Internal Power Dissipation (Measured at T <sub>A</sub> = T <sub>L</sub> in Steady-S               | State Operation)                    | PINT                                | _                                            | 1200                 | _                                            | 1500                  | _                                            | 1500                 | mW   |

| Input Capacitance $(V_{in} = 0, T_A = 25^{\circ}C, f_0 = 1.0 \text{ MHz})$                        | Port 3, Port 4, SCI<br>Other Inputs | C <sub>in</sub>                     | -                                            | 12.5<br>10           | _                                            | 12.5<br>10            | -                                            | 12.5<br>10           | pF   |

| V <sub>CC</sub> Standby                                                                           | Powerdown<br>Powerup                | V <sub>SBB</sub><br>V <sub>SB</sub> | 4.0<br>4.75                                  | 5.25<br>5.25         | 4.0<br>4.75                                  | 5.25<br>5.25          | 4.0<br>4.75                                  | 5.25<br>5.25         | V    |

| Standby Current                                                                                   | Powerdown                           | ISBB                                | -                                            | 6.0                  | _                                            | 8.0                   | _                                            | 8.0                  | mΑ   |

<sup>\*</sup>Negotiable to  $-100 \mu A$  (for further information contact the factory)

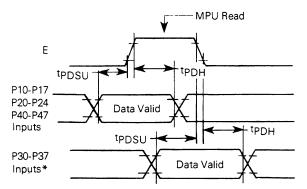

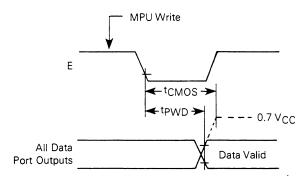

#### PERIPHERAL PORT TIMING (Refer to Figures 2-5)

|                                                                      |                   | MC6801<br>MC6803 |     | MC6801-1<br>MC6803-1 |     | MC68A01<br>MC68A03 |     | MC68B01<br>MC68B03 |     |      |

|----------------------------------------------------------------------|-------------------|------------------|-----|----------------------|-----|--------------------|-----|--------------------|-----|------|

| Characteristics                                                      | Symbol            | Min              | Max | Min                  | Max | Min                | Max | Min                | Max | Unit |

| Peripheral Data Setup Time                                           | <sup>t</sup> PDSU | 200              | -   | 200                  | _   | 150                | _   | 100                | -   | ns   |

| Peripheral Data Hold Time                                            | <sup>t</sup> PDH  | 200              | _   | 200                  | -   | 150                | _   | 100                | _   | ns   |

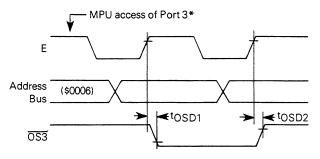

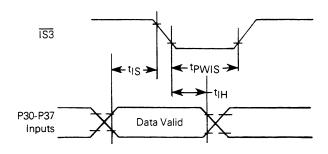

| Delay Time, Enable Positive Transition to OS3 Negative Transition    | tOSD1             | _                | 350 | -                    | 350 | Ļ                  | 300 | _                  | 250 | ns   |

| Delay Time, Enable Positive Transition to OS3 Positive Transition    | tOSD2             | -                | 350 | _                    | 350 | -                  | 300 | -                  | 250 | ns   |

| Delay Time, Enable Negative Transition to Peripheral Data Valid      | tPWD              | _                | 350 | _                    | 350 | _                  | 300 | -                  | 250 | ns   |

| Delay Time, Enable Negative Transition to Peripheral CMOS Data Valid | <sup>t</sup> CMOS | _                | 2.0 | _                    | 2.0 | _                  | 2.0 | -                  | 2.0 | μS   |

| Input Strobe Pulse Width                                             | <sup>t</sup> PWIS | 200              | -   | 200                  | _   | 150                | _   | 100                | _   | ns   |

| Input Data Hold Time                                                 | tιΗ               | 50               | _   | 50                   | _   | 40                 | _   | 30                 | _   | ns   |

| Input Data Setup Time                                                | t <sub>IS</sub>   | 20               | -   | 20                   | _   | 20                 |     | 20                 | _   | ns   |

FIGURE 2 — DATA SETUP AND HOLD TIMES (MPU READ)

\*Port 3 non-latched operation (LATCH ENABLE=0)

FIGURE 3 — DATA SETUP AND HOLD TIMES (MPU WRITE)

#### NOTES:

- 1. 10 k pullup resistor required for port 2 to reach 0.7 V<sub>CC</sub>.

- 2. Not applicable to P21.

- 3. Port 4 cannot be pulled above VCC.

FIGURE 4 — PORT 3 OUTPUT STROBE TIMING (MC6801 SINGLE-CHIP MODE)

\* Access matches output strobe select (OSS = 0, a read; OSS = 1, a write)

# FIGURE 5 — PORT 3 LATCH TIMING (MC6801 SINGLE-CHIP MODE)

NOTE: Timing measurements are referenced to and from a low voltage of 0.8 volts and a high voltage of 2.0 volts, unless otherwise noted.

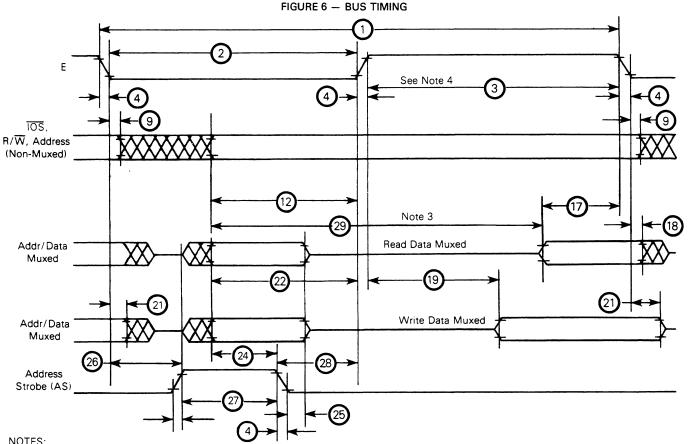

#### BUS TIMING (See Notes 1 and 2)

| Ident.<br>Number | Characteristics                      | Symbol                          | MC6801<br>MC6803 |          | MC6801-1<br>MC6803-1 |      | MC68A01<br>MC68A03 |      | MC68B01<br>MC68B03 |      | Unit |

|------------------|--------------------------------------|---------------------------------|------------------|----------|----------------------|------|--------------------|------|--------------------|------|------|

| Number           |                                      |                                 | Min              | Max      | Min                  | Max  | Min                | Max  | Min                | Max  |      |

| 1                | Cycle Time                           | tcyc                            | 1.0              | 2.0      | 0.8                  | 2.0  | 0.667              | 2.0  | 0.5                | 2.0  | μS   |

| 2                | Pulse Width, E Low                   | PWEL                            | 430              | 1000     | 360                  | 1000 | 300                | 1000 | 210                | 1000 | ns   |

| 3                | Pulse Width, E High                  | PWEH                            | 450              | 1000     | 360                  | 1000 | 300                | 1000 | 220                | 1000 | ns   |

| 4                | Clock Rise and Fall Time             | t <sub>r</sub> , t <sub>f</sub> | T -              | 25       | _                    | 25   | _                  | 25   | _                  | 20   | ns   |

| 9                | Address Hold Time                    | t <sub>A</sub> H                | 20               | _        | 20                   | _    | 20                 | _    | 10                 | _    | ns   |

| 12               | Non-Muxed Address Valid Time to E*   | t <sub>AV</sub>                 | 200              | _        | 150                  | _    | 115                | _    | 70                 | _    | ns   |

| 17               | Read Data Setup Time                 | †DSR                            | 80               | -        | 70                   | _    | 60                 | -    | 40                 | _    | ns   |

| 18               | Read Data Hold Time                  | <sup>t</sup> DHR                | 10               | _        | 10                   | _    | 10                 | _    | 10                 | _    | ns   |

| 19               | Write Data Delay Time                | tDDW                            | -                | 225      | _                    | 200  | _                  | 170  | _                  | 120  | ns   |

| 21               | Write Data Hold Time                 | tDHW                            | 20               | _        | 20                   |      | 20                 | _    | 10                 | _    | ns   |

| 22               | Muxed Address Valid Time to E Rise*  | <sup>t</sup> AVM                | 200              | -        | 150                  | _    | 115                | _    | 80                 | _    | ns   |

| 24               | Muxed Address Valid Time to AS Fall* | †ASL                            | 60               | _        | 50                   | _    | 40                 | -    | 20                 | _    | ns   |

| 25               | Muxed Address Hold Time              | †AHL                            | 20               | _        | 20                   | _    | 20                 | _    | 10                 | _    | ns   |

| 26               | Delay Time, E to AS Rise*            | tASD                            | 90**             | _        | 70**                 | _    | 60**               | -    | 45**               | _    | ns   |

| 27               | Pulse Width, AS High*                | PWASH                           | 220              | <u> </u> | 170                  | _    | 140                | _    | 110                | -    | ns   |

| 28               | Delay Time, AS to E Rise*            | †ASED                           | 90               | _        | 70                   | _    | 60                 | -    | 45                 | -    | ns   |

| 29               | Usable Access Time*                  | †ACC                            | 595              | -        | 465                  | _    | 380                | _    | 270                | _    | ns   |

<sup>\*</sup> At specified cycle time.

<sup>\*\*</sup>tasp parameters listed assume external TTL clock drive with 50% ±5% duty cycle. Devices driven by an external TTL clock with 50%  $\pm\,1\%$  duty cycle or which use a crystal have the following t<sub>ASD</sub> specifications: 100 nanoseconds minimum (1.0 MHz devices), 80 nanoseconds minimum (1.25 MHz device), 65 nanoseconds minimum (1.5 MHz devices), 50 nanoseconds minimum (2.0 MHz devices).

#### NOTES:

- 1. Voltage levels shown are VL  $\leq$  0.5 V, VH  $\geq$  2.4 V, unless otherwise specified.

- 2. Measurement points shown are 0.8 V and 2.0 V, unless otherwise specified.

- 3. Usable access time is computed by: 12+3-17+4.

- 4. Memory devices should be enabled only during E high to avoid port 3 bus contention.

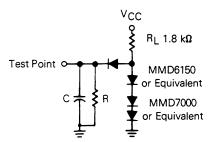

#### FIGURE 7 - CMOS LOAD

# Test Point o 30 pF

#### FIGURE 8 - TIMING TEST LOAD PORTS 1, 2, 3, 4

C=90 pF for P30-P37, P40-P47, E, SC1, SC2 =30 pF for P10-P17, P20-P24 R=37 k $\Omega$  for P40-P47, SC1, SC2 = 24 k $\Omega$  for P10-P17, P20-P24 = 24 k $\Omega$  for P30-P37, E

#### INTRODUCTION

The MC6801 is an 8-bit monolithic microcomputer which can be configured to function in a wide variety of applications. The facility which provides this extraordinary flexibility is its ability to be hardware programmed into eight different operating modes. The operating mode controls the configuration of 18 of the 40 MCU pins, available on-chip resources, memory map, location (internal or external) of interrupt vectors, and type of external bus. The configuration of the remaining 22 pins is not dependent on the operating mode.

Twenty-nine pins are organized as three 8-bit ports and one 5-bit port. Each port consists of at least a data register and a write-only data direction register. The data direction register is used to define whether corresponding bits in the data register are configured as an input (clear) or output (set).

The term "port," by itself, refers to all of the hardware associated with the port. When the port is used as a "data port" or "I/O port," it is controlled by the port data direction register and the programmer has direct access to the port pins using the port data register. Port pins are labeled as Pij where i identifies one of four ports and j indicates the particular bit.

The microprocessor unit (MPU) is an enhanced MC6800 MPU with additional capabilities and greater throughput. It is upward source and object code compatible with the MC6800. The programming model is depicted in Figure 9, where accumulator D is a concatenation of accumulators A and B. A list of new operations added to the M6800 instruction set are shown in Table 1.

The MC6803 can be considered an MC6801 that operates in Modes 2 and 3 only.

#### FIGURE 9 - PROGRAMMING MODEL 8-Bit Accumulators A and B Or 16-Bit Double Accumulator D D 15 Index Register (X) Х 15 Stack Pointer (SP) SP PC Program Counter (PC) Condition Code Register (CCR) Ν Carry/Borrow from MSB Overflow Zero Negative Interrupt Half Carry (From Bit 3)

#### **OPERATING MODES**

The MC6801 provides eight different operating modes (0 through 7) and the MC6803 provides two operating modes (2 and 3). The operating modes are hardware selectable and determine the device memory map, the configuration of port 3, port 4, SC1, SC2, and the physical location of the interrupt vectors.

#### **FUNDAMENTAL MODES**

The eight operating modes can be grouped into three fundamental modes which refer to the type of bus it supports: single chip, expanded non-multiplexed, and expanded multiplexed. Single-chip modes include 4 and 7, expanded non-multiplexed mode is 5, and the remaining five modes are

expanded multiplexed modes. Table 2 summarizes the characteristics of the operating modes.

#### MC6801 Single-Chip Modes (4, 7)

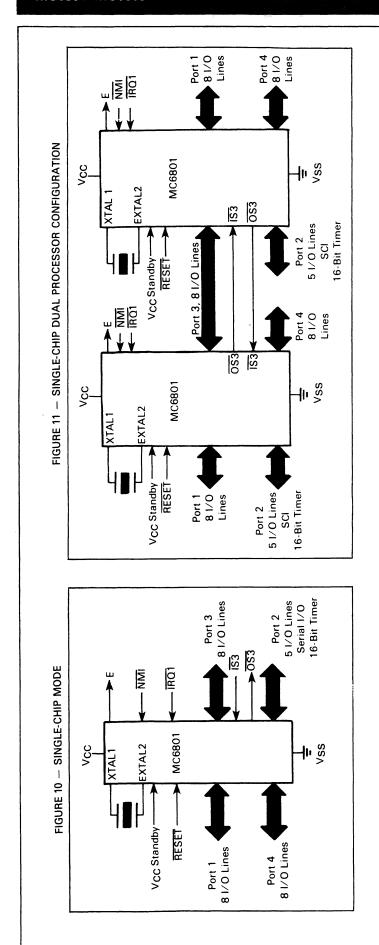

In the single-chip mode, the four MCU ports are configured as parallel input/output data ports, as shown in Figure 10. The MCU functions as a monolithic microcomputer in these two modes without external address or data buses. A maximum of 29 I/O lines and two port 3 control lines are provided. Peripherals or another MCU can be interfaced to port 3 in a loosely coupled dual processor configuration, as shown in Figure 11.

TABLE 1 - NEW INSTRUCTIONS

| Instruction  | Description                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| ABX          | Unsigned addition of accumulator B to index register                                                                            |

| ADDD         | Adds (without carry) the double accumulator to memory and leaves the sum in the double accumulator                              |

| ASLD or LSLD | Shifts the double accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C bit              |

| BHS          | Branch if higher or same; unsigned conditional branch (same as BCC)                                                             |

| BLO          | Branch if lower; unsigned conditional branch (same as BCS)                                                                      |

| BRN          | Branch never                                                                                                                    |

| JSR          | Additional addressing mode: direct                                                                                              |

| LDD          | Loads double accumulator from memory                                                                                            |

| LSL          | Shifts memory or accumulator left (towards MSB) one bit; the LSB is cleared and the MSB is shifted into the C bit (same as ASL) |

| LSRD         | Shifts the double accumulator right (towards LSB) one bit; the MSB is cleared and the LSB is shifted into the C bit             |

| MUL          | Unsigned multiply; multiplies the two accumulators and leaves the product in the double accumulator                             |

| PSHX         | Pushes the index register to stack                                                                                              |

| PULX         | Pulls the index register from stack                                                                                             |

| STD          | Stores the double accumulator to memory                                                                                         |

| SUBD         | Subtracts memory from the double accumulator and leaves the difference in the double accumulator                                |

| CPX          | Internal processing modified to permit its use with any conditional branch instruction                                          |

In single-chip test mode (4), the RAM responds to \$XX80 through \$XXFF and the ROM is removed from the internal address map. A test program must first be loaded into the RAM using modes 0, 1, 2, or 6. If the MCU is reset and then programmed into mode 4, execution will begin at \$XXFE:XXFF. Mode 5 can be irreversibly entered from mode 4 without asserting RESET by setting bit 5 of the port 2 data register. This mode is used primarily to test ports 3 and 4 in the single-chip and non-multiplexed modes.

#### MC6801 Expanded Non-Multiplexed Mode (5)

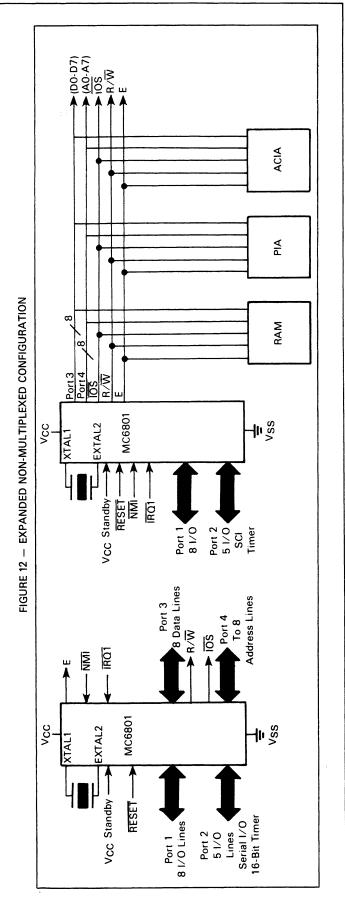

A modest amount of external memory space is provided in the expanded non-multiplexed mode while significant onchip resources are retained. Port 3 functions as an 8-bit bidirectional data bus and port 4 is configured initially as an input data port. Any combination of the eight least-significant address lines may be obtained by writing to the port 4 data direction register. Stated alternatively, any combination of A0 to A7 may be provided while retaining the remainder as input data lines. Internal pullup resistors pull the port 4 lines high until the port is configured.

Figure 12 illustrates a typical system configuration in the expanded non-multiplexed mode. The MCU interfaces directly with M6800 Family parts and can access 256 bytes of external address space at \$100 through \$1FF. IOS provides an address decode of external memory (\$100-\$1FF) and can be used as a memory-page select or chip-select line.

#### TABLE 2 - SUMMARY OF MC6801/03 OPERATING MODES

#### Common to all Modes:

Reserved Register Area

Port 1

Port 2

Programmable Timer

Serial Communications Interface

#### Single Chip Mode 7

128 bytes of RAM; 2048 bytes of ROM

Port 3 is a parallel I/O port with two control lines

Port 4 is a parallel I/O port

SC1 is Input Strobe 3 (IS3)

SC2 is Output Strobe 3 (OS3)

#### Expanded Non-Multiplexed Mode 5

128 bytes of RAM; 2048 bytes of ROM

256 bytes of external memory space

Port 3 is an 8-bit data bus

Port 4 is an input port/address bus

SC1 is Input/Output Select (IOS)

SC2 is Read/Write  $(R/\overline{W})$

#### Expanded Multiplexed Modes 1, 2, 3, 6\*

Four memory space options (64K address space):

- (1) No internal RAM or ROM (Mode 3)

- (2) Internal RAM, no ROM (Mode 2)

- (3) Internal RAM and ROM (Mode 1)

- (4) Internal RAM, ROM with partial address bus (Mode 6)

Port 3 is a multiplexed address/data bus

Port 4 is an address bus (inputs/address in Mode 6)

SC1 is Address Strobe (AS)

SC2 is Read/Write (R/W)

#### Test Modes 0 and 4

Expanded Multiplexed Test Mode 0

May be used to test RAM and ROM

Single Chip and Non-Multiplexed Test Mode 4

- (1) May be changed to Mode 5 without going through Reset

- (2) May be used to test Ports 3 and 4 as I/O ports

<sup>\*</sup>The MC6803 operates only in modes 2 and 3.

#### Expanded-Multiplexed Modes (0, 1, 2, 3, 6)

A 64K byte memory space is provided in the expanded-multiplexed modes. In each of the expanded-multiplexed modes port 3 functions as a time multiplexed address/data bus with address valid on the negative edge of address strobe (AS), and data valid while E is high. In modes 0 to 3, port 4 provides address lines A8 to A15. In mode 6, however, port 4 initially is configured at RESET as an input data port. The port 4 data direction register can then be changed to provide any combination of address lines, A8 to A15. Stated alternatively, any subset of A8 to A15 can be provided while retaining the remaining port 4 lines as input data lines. Internal pullup resistors pull the port 4 lines high until software configures the port.

In mode 0, the reset vector is external for the first two E cycles after the positive edge of  $\overline{\text{RESET}}$ , and internal thereafter. In addition, the internal and external data buses are connected so there must be no memory map overlap in order to avoid potential bus conflicts. Mode 0 is used primarily to verify the ROM pattern and monitor the internal data bus with the automated test equipment.

Only the MC6801 can operate in each of the expanded-multiplexed modes. The MC6803 operates only in modes 2 and 3.

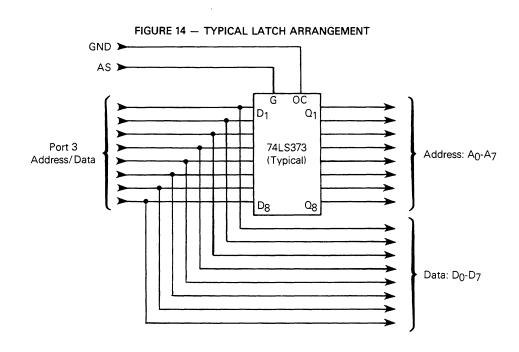

Figure 13 depicts a typical configuration for the expandedmultiplexed modes. Address strobe can be used to control a transparent D-type latch to capture addresses A0-A7, as shown in Figure 14. This allows port 3 to function as a data bus when E is high.

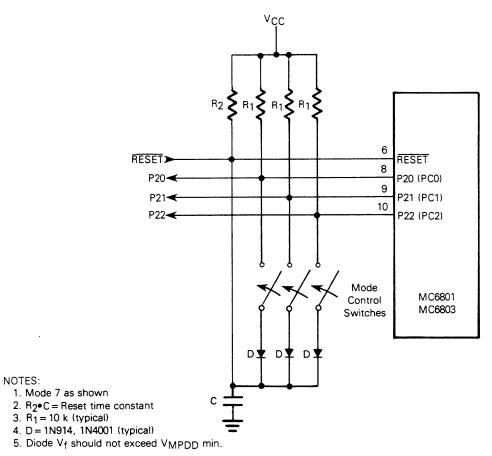

#### PROGRAMMING THE MODE

The operating mode is determined at  $\overline{\text{RESET}}$  by the levels asserted on P22, P21, and P20. These levels are latched into PC2, PC1, and PC0 of the program control register on the positive edge of  $\overline{\text{RESET}}$ . The operating mode may be read from the port 2 data register as shown below, and programming levels and timing must be met as shown in Figure 15. A brief outline of the operating modes is shown in Table 3.

#### **PORT 2 DATA REGISTER**

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |        |

|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| PC2 | PC1 | PC0 | P24 | P23 | P22 | P21 | P20 | \$0003 |

Circuitry to provide the programming levels is dependent primarily on the normal system usage of the three pins. If configured as outputs, the circuit shown in Figure 16 may be used; otherwise, three-state buffers can be used to provide isolation while programming the mode.

#### TABLE 3 - MODE SELECTION SUMMARY

| Mode* | P22<br>PC2 | P21<br>PC1 | P20<br>PC0 | ROM  | RAM  | Interrupt<br>Vectors | Bus<br>Mode           | Operating<br>Mode              |

|-------|------------|------------|------------|------|------|----------------------|-----------------------|--------------------------------|

| 7     | Н          | Н          | Н          | 1    | ı    | I                    | 1                     | Single Chip                    |

| 6     | Н          | Н          | L          | 1    | ı    | 1                    | MUX <sup>(5, 6)</sup> | Multiplexed/Partial Decode     |

| 5     | Н          | L          | Н          | ı    |      | 1                    | MUX <sup>(5, 6)</sup> | Non-Multiplexed/Partial Decode |

| 4     | Н          | L          | L          | J(2) | j(1) | 1                    | 1                     | Single-Chip Test               |

| 3     | L          | Н          | н          | E    | E    | E                    | M∪X <sup>(4)</sup>    | Multiplexed/No RAM or ROM      |

| 2     | L          | Н          | L          | E    | ı    | E                    | M∪X <sup>(4)</sup>    | Multiplexed/RAM                |

| 1     | L          | L          | Н          | 1    | 1    | E                    | MUX <sup>(4)</sup>    | Multiplexed/RAM and ROM        |

| 0     | L          | L          | L          | 1    | ı    | Į(3)                 | MUX <sup>(4)</sup>    | Multiplexed Test               |

#### Legend:

I — Internal

E - External

MUX - Multiplexed

NMUX - Non-Multiplexed

L - Logic Zero

H - Logic One

#### NOTES:

- (1) Internal RAM is addressed at \$XX80.

- (2) Internal ROM is disabled.

- (3)  $\overline{\text{RESET}}$  vector is external for two cycles after  $\overline{\text{RESET}}$  goes high.

- (4) Addresses associated with ports 3 and 4 are considered external in modes 0, 1, 2, and 3.

- (5) Addresses associated with port 3 are considered external in modes 5 and 6.

- (6) Port 4 default is user data input; address output is optional by writing to port 4 data direction register.

<sup>\*</sup>The MC6803 operates only in modes 2 and 3.

FIGURE 13 — EXPANDED MULTIPLEXED CONFIGURATION Vcc XTAL1 **→** E NMI EXTAL2 V<sub>CC</sub> Standby RESET IRQ1 MC6801 MC6803 Port 1 Port 3 8 Lines 8 I/O Lines Multiplexed Data/Address R/W Port 2 -AS Port 4 5 I/O Lines 8 Lines Serial I/O Address Bus 16-Bit Timer Ţ √SS  $V_{CC}$ XTAL1 Port 3 Data Bus (D0-D7) EXTAL2 Latch V<sub>CC</sub> Standby Address Bus RESET (A0-A15) NMI MC6801 16  $R/\overline{W}$ **IRQ1** ►R/W MC6803 Port 1 8 1/0 Port 2 5 1/0 SCI Timer Ţ vss ROM RAM PIA

NOTE: To avoid data bus (port 3) contention in the expanded multiplexed modes, memory devices should be enabled only during E high time.

**MOTOROLA** Semiconductor Products Inc.

# FIGURE 15 – MODE PROGRAMMING TIMING See Figure 16 for Diode Arrangement VMPDD VMPL VMPH Min (P20, P21, P22) VMPL VMPL Mode Latch Level

#### MODE PROGRAMMING (Refer to Figure 15)

| Characteristic                                           | Symbol           | Min | Max | Unit     |

|----------------------------------------------------------|------------------|-----|-----|----------|

| Mode Programming Input Voltage Low*                      | VMPL             | _   | 1.8 | V        |

| Mode Programming Input Voltage High                      | VMPH             | 4.0 | _   | V        |

| Mode Programming Diode Differential (If Diodes are Used) | VMPDD            | 0.6 | _   | V        |

| RESET Low Pulse Width                                    | PWRSTL           | 3.0 | -   | E Cycles |

| Mode Programming Setup Time                              | tMPS             | 2.0 | _   | E Cycles |

| Mode Programming Hold Time                               |                  |     |     |          |

| RESET Rise Time≥1 μs                                     | t <sub>MPH</sub> | 0   | -   | ns       |

| RESET Rise Time < 1 μs                                   | 1                | 100 | l   |          |

<sup>\*</sup>For  $T_A = -40$ °C to 105°C,  $V_{MPL} = 1.7 \text{ V}$ .

#### FIGURE 16 - TYPICAL MODE PROGRAMMING CIRCUIT

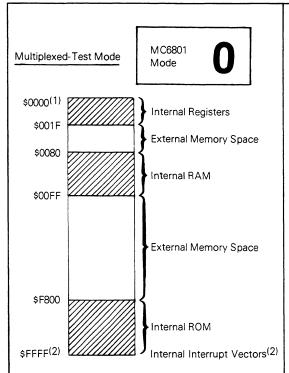

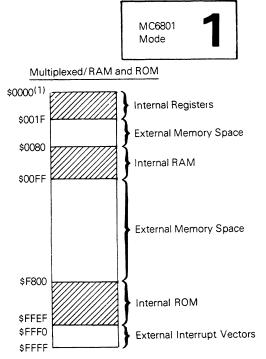

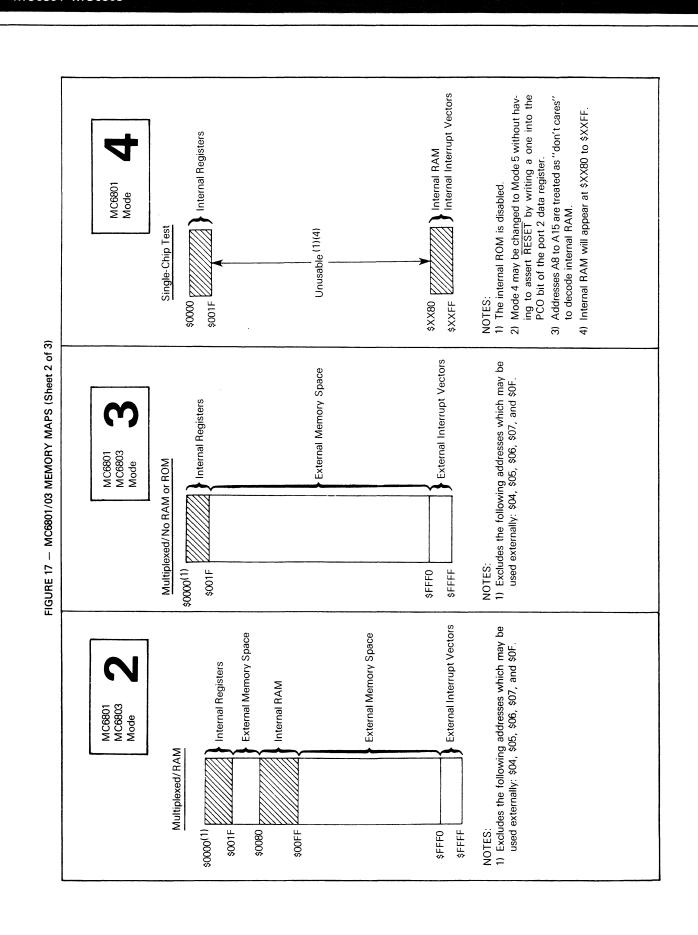

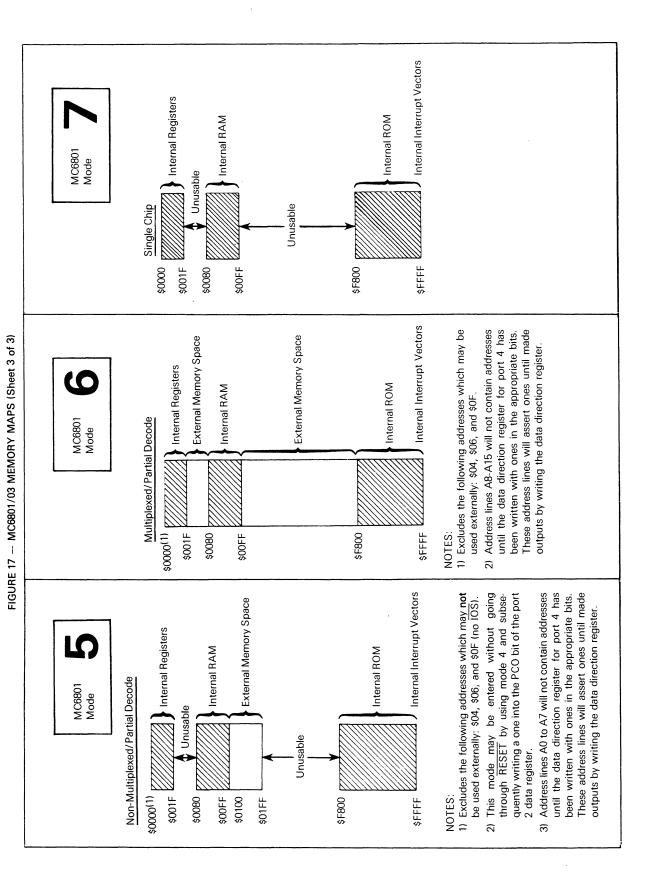

#### **MEMORY MAPS**

The M6801 Family can provide up to 64K byte address space depending on the operating mode. A memory map for

each operating mode is shown in Figure 17. The first 32 locations of each map are reserved for the internal register area, as shown in Table 4, with exceptions as indicated.

**MOTOROLA** Semiconductor Products Inc.

FIGURE 17 - MC6801/03 MEMORY MAPS (Sheet 1 of 3)

#### NOTES:

- 1) Excludes the following addresses which may be used externally: \$04, \$05, \$06, \$07, and \$0F.

- Addresses \$FFFE and \$FFFF are considered external if accessed within two cycles after a positive edge of RESET and internal at all other times.

- After two MPU cycles, there must be no overlapping of internal and external memory spaces to avoid driving the data bus with more than one device.

- 4) This mode is the only mode which may be used to examine the interrupt vectors in internal ROM using an external RESET vector.

#### NOTES:

- 1) Excludes the following addresses which may be used externally: \$04, \$05, \$06, \$07, and \$0F.

- 2) Internal ROM addresses \$FFF0 to \$FFFF are not usable.

#### MC6801/03 INTERRUPTS

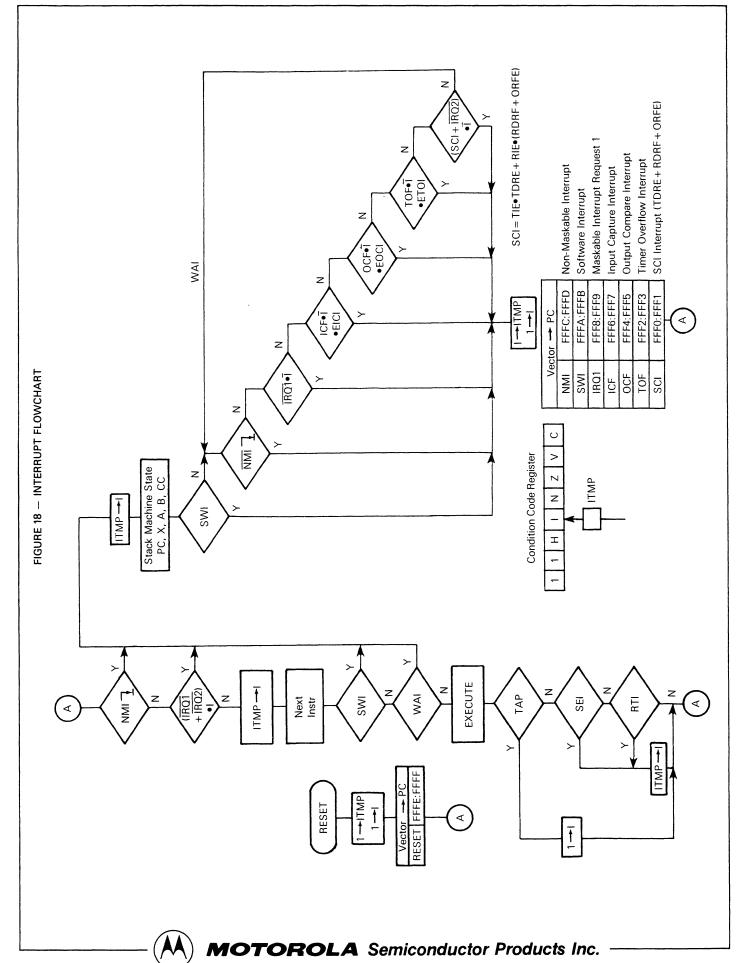

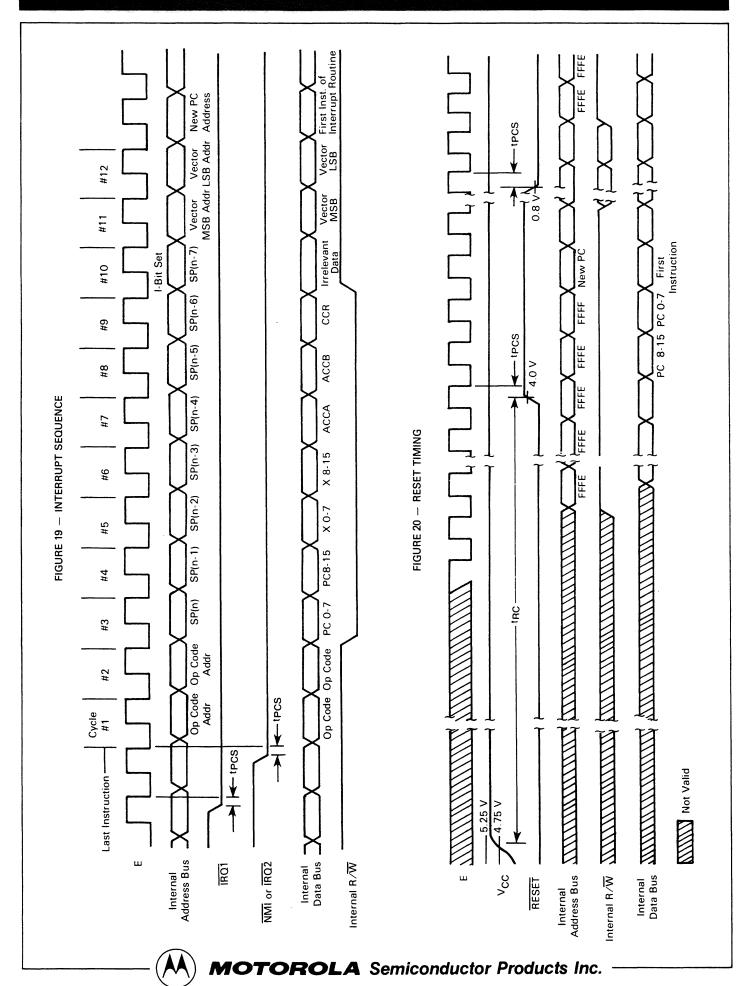

The M6801 Family supports two types of interrupt requests: maskable and non-maskable. A non-maskable interrupt ( $\overline{NMI}$ ) is always recognized and acted upon at the completion of the current instruction. Maskable interrupts are controlled by the condition code register I bit and by individual enable bits. The I bit controls all maskable interrupts. Of the maskable interrupts, there are two types:  $\overline{IRQ1}$  and  $\overline{IRQ2}$ . The programmable timer and serial communications interface use an internal  $\overline{IRQ2}$  interrupt line, as shown in Figure 1. External devices (and IS3) use  $\overline{IRQ1}$ . An  $\overline{IRQ1}$  interrupt is serviced before  $\overline{IRQ2}$  if both are pending.

All IRO2 interrupts use hardware prioritized vectors. The single SCI interrupt and three timer interrupts are serviced in a prioritized order and each is vectored to a separate location. All interrupt vector locations are shown in Table 5.

The interrupt flowchart is depicted in Figure 18 and is common to every interrupt excluding reset. During interrupt servicing the program counter, index register, A accumulator, B accumulator, and condition code register are pushed to the stack. The I bit is set to inhibit maskable interrupts and a vector is fetched corresponding to the current highest priority interrupt. The vector is transferred to the program counter and instruction execution is resumed. Interrupt and RESET timing are illustrated in Figures 19 and 20.

#### **FUNCTIONAL PIN DESCRIPTIONS**

#### VCC AND VSS

VCC and VSS provide power to a large portion of the MCU. The power supply should provide  $\pm 5$  volts ( $\pm 5\%$ ) to VCC, and VSS should be tied to ground. Total power dissipation (including VCC standby), will not exceed PD milliwatts.

#### VCC STANDBY

VCC standby provides power to the standby portion (\$80 through \$BF) of the RAM and the STBY PWR and RAME bits of the RAM control register. Voltage requirements depend on whether the device is in a powerup or powerdown state. In the powerup state, the power supply should provide +5 volts ( $\pm\,5\%$ ) and must reach VSB volts before  $\overline{\text{RESET}}$  reaches 4.0 volts. During powerdown, VCC standby must remain above VSBB (min) to sustain the standby RAM and STBY PWR bit. While in powerdown operation, the standby current will not exceed ISBB.

It is typical to power both VCC and VCC standby from the same source during normal operation. A diode must be used

between them to prevent supplying power to  $V_{CC}$  during powerdown operation.  $V_{CC}$  standby should be tied to ground in mode 3.

TABLE 4 - INTERNAL REGISTER AREA

| Register                                     | Address |

|----------------------------------------------|---------|

| Port 1 Data Direction Register* * *          | 00      |

| Port 2 Data Direction Register* * *          | 01      |

| Port 1 Data Register                         | 02      |

| Port 2 Data Register                         | 03      |

| Port 3 Data Direction Register* * *          | 04*     |

| Port 4 Data Direction Register*.* *          | 05**    |

| Port 3 Data Register                         | 06*     |

| Port 4 Data Register                         | 07**    |

| Timer Control and Status Register            | 08      |

| Counter (High Byte)                          | 09      |

| Counter (Low Byte)                           | 0A      |

| Output Compare Register (High Byte)          | 0B      |

| Output Compare Register (Low Byte)           | 0C      |

| Input Capture Register (High Byte)           | 0D      |

| Input Capture Register (Low Byte)            | 0E      |

| Port 3 Control and Status Register           | OF*     |

| Rate and Mode Control Register               | 10      |

| Transmit/Receive Control and Status Register | 11      |

| Receive Data Register                        | 12      |

| Transmit Data Register                       | 13      |

| RAM Control Register                         | 14      |

| Reserved                                     | 15-1F   |

<sup>\*</sup>External addresses in modes 0, 1, 2, 3, 5, and 6; cannot be accessed in mode 5 (no  $\overline{\text{IOS}}$ ).

TABLE 5 - MCU INTERRUPT VECTOR LOCATIONS

| MSB  | LSB  | Interrupt                |

|------|------|--------------------------|

| FFFE | FFFF | RESET                    |

| FFFC | FFFD | NMI                      |

| FFFA | FFFB | Software Interrupt (SWI) |

| FFF8 | FFF9 | IRQ1 (or IS3)            |

| FFF6 | FFF7 | ICF (Input Capture)*     |

| FFF4 | FFF5 | OCF (Output Capture)*    |

| FFF2 | FFF3 | TOF (Timer Overflow)*    |

| FFF0 | FFF1 | SCI (RDRF+ORFE+TDRE)*    |

<sup>\*</sup> IRQ2 Interrupt

<sup>\* \*</sup> External addresses in modes 0, 1, 2, and 3.

<sup>\* \* \* 1 =</sup> Output, 0 = Input.

17

#### XTAL1 AND EXTAL2

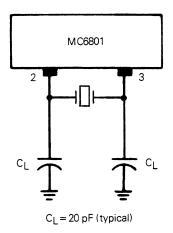

These two input pins interface either a crystal or TTL compatible clock to the MCU internal clock generator. Divide-by-four circuitry is included which allows use of the inexpensive 3.58 MHz or 4.4336 MHz Color Burst TV crystals. A 20 pF capacitor should be tied from each crystal pin to ground to ensure reliable startup and operation. Alternatively, EXTAL2 may be driven by an external TTL compatible clock at  $4f_0$  with a duty cycle of 50% ( $\pm\,5\%$ ) with XTAL1 connected to ground.

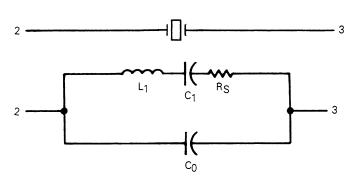

The internal oscillator is designed to interface with an AT-cut quartz crystal resonator operated in parallel resonance mode in the frequency range specified for  $f_{\rm XTAL}.$  The crystal should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time.\* The MCU is compatible with most commercially available crystals. Nominal crystal parameters are shown in Figure 21.

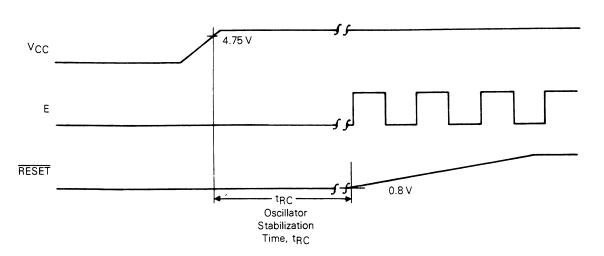

#### RESET

This input is used to reset the internal state of the device and provide an orderly startup procedure. During powerup, RESET must be held below 0.8 volts: (1) at least t<sub>RC</sub> after V<sub>CC</sub> reaches 4.75 volts in order to provide sufficient time for the clock generator to stabilize, and (2) until V<sub>CC</sub> standby reaches 4.75 volts. RESET must be held low at least three E cycles if asserted during powerup operation.

#### E (ENABLE)

This is an output clock used primarily for bus synchronization. It is TTL compatible and is the slightly skewed divide-by-four result of the device input clock frequency. It will drive one Schottky TTL load and 90 pF, and all data given in cycles is referenced to this clock unless otherwise noted.

#### NON-MASKABLE INTERRUPT (NMI)

An  $\overline{\text{NMI}}$  negative edge requests an MCU interrupt sequence, but the current instruction will be completed before it responds to the request. The MCU will then begin an interrupt sequence. Finally, a vector is fetched from \$FFFC and \$FFFD, transferred to the program counter and instruction execution is resumed.  $\overline{\text{NMI}}$  typically requires a 3.3 k $\Omega$  (nominal) resistor to VCC. There is no internal  $\overline{\text{NMI}}$  pullup resistor.  $\overline{\text{NMI}}$  must be held low for at least one E cycle to be recognized under all conditions.

#### MASKABLE INTERRUPT REQUEST 1 (IRQ1)

IRQ1 is a level-sensitive input which can be used to request an interrupt sequence. The MPU will complete the current instruction before it responds to the request. If the interrupt mask bit (I bit) in the condition code register is clear, the MCU will begin an interrupt sequence. A vector is fetched from \$FFF8 and \$FFF9, transferred to the program counter, and instruction execution is resumed.

$\overline{1RQ1}$  typically requires an external 3.3 k $\Omega$  (nominal) resistor to VCC for wire-OR applications.  $\overline{1RQ1}$  has no internal pullup resistor.

#### STROBE CONTROL 1 AND 2 (SC1 AND SC2)

The function of SC1 and SC2 depends on the operating mode. SC1 is configured as an output in all modes except single-chip mode, whereas SC2 is always an output. SC1 and SC2 can drive one Schottky load and 90 pF.

#### SC1 and SC2 In Single-Chip Mode

In single-chip mode, SC1 and SC2 are configured as an input and output, respectively, and both function as port 3 control lines. SC1 functions as  $\overline{1S3}$  and can be used to indicate that port 3 input data is ready or output data has been accepted. Three options associated with  $\overline{1S3}$  are controlled by port 3 control and status register and are discussed in the PORT 3 (P30-P37). If unused,  $\overline{1S3}$  can remain unconnected.

SC2 is configured as  $\overline{OS3}$  and can be used to strobe output data or acknowledge input data. It is controlled by output strobe select (OSS) in the port 3 control and status register. The strobe is generated by a read (OSS=0) or write (OSS=1) to the port 3 data register.  $\overline{OS3}$  timing is shown in Figure 4.

#### SC1 and SC2 In Expanded Non-Multiplexed Mode

In the expanded non-multiplexed mode, both SC1 and SC2 are configured as outputs. SC1 functions as input/output select ( $\overline{\text{IOS}}$ ) and is asserted only when \$0100 through \$01FF is sensed on the internal address bus.

SC2 is configured as read/write and is used to control the direction of data bus transfers. An MPU read is enabled when read/write and E are high.

#### SC1 and SC2 In Expanded-Multiplexed Mode

In the expanded-multiplexed mode, both SC1 and SC2 are configured as outputs. SC1 functions as address strobe and can be used to demultiplex the eight least-significant addresses and the data bus. A latch controlled by address strobe captures address on the negative edge, as shown in Figure 14.

SC2 is configured as read/write and is used to control the direction of data bus transfers. An MPU read is enabled when read/write and E are high.

#### PORT 1 (P10-P17)

Port 1 is a mode independent 8-bit I/O port with each line an input or output as defined by the port 1 data direction register. The TTL compatible three-state output buffers can drive one Schottky TTL load and 30 pF, Darlington transistors, or CMOS devices using external pullup resistors. It is configured as a data input port by RESET. Unused lines can remain unconnected.

#### PORT 2 (P20-P24)

#### **PORT 2 DATA REGISTER**

| 7   | 6   | 5   | 4   | 3   | 2   | 1_  | 0   |        |

|-----|-----|-----|-----|-----|-----|-----|-----|--------|

| PC2 | PC1 | PC0 | P24 | P23 | P22 | P21 | P20 | \$0003 |

Port 2 is a mode-independent, 5-bit, multi-purpose I/O port. The voltage levels present on P20, P21, and P22 on the rising edge of RESET determine the operating mode of the MCU. The entire port is then configured as a data input port. The port 2 lines can be selectively configured as data output lines by setting the appropriate bits in the port 2 data direction register. The port 2 data register is used to move data through the port. However, if P21 is configured as an output, it will be tied to the timer output compare function and cannot be used to provide output from the port 2 data register.

<sup>\*</sup>Devices made with masks subsequent to M5G, M8D, and T5P incorporate an advanced clock with improved startup characteristics.

#### FIGURE 21 - M6801 FAMILY OSCILLATOR CHARACTERISTICS

#### (a) Nominal Recommended Crystal Parameters

#### Nominal Crystal Parameters\*

|       | 3.58 MHz | 4.00 MHz | 5.0 MHz      | 6.0 MHz      | 8.0 MHz      |

|-------|----------|----------|--------------|--------------|--------------|

| RS    | 60 Ω     | 50 Ω     | 30-50 Ω      | 30-50 Ω      | 20-40 Ω      |

| $c_0$ | 3.5 pF   | 6.5 pF   | 4-6 pF       | 4-6 pF       | 4-6 pF       |

| $C_1$ | 0.015 pF | 0.025 pF | 0.01-0.02 pF | 0.01-0.02 pF | 0.01-0.02 pF |

| Q     | >40 K    | >30 K    | >20 K        | >20 K        | >20 K        |

<sup>\*</sup> NOTE: These are representative AT-cut crystal parameters only. Crystals of other types of cut may also be used.

Equivalent Circuit

#### NOTE

TTL-compatible oscillators may be obtained from:

Motorola Component Products Attn: Data Clock Sales 2553 N. Edgington St. Franklin Park, IL 60131 Tel: 312-451-1000

Tel: 312-451-1000 Telex: 433-0067

#### (b) Oscillator Stabilization Time (tRC)

Port 2 can also be used to provide an interface for the serial communications interface and the timer input edge function. These configurations are described in PROGRAM-MABLE TIMER and SERIAL COMMUNICATIONS INTERFACE (SCI).

The port 2 high-impedance TTL-compatible output buffers are capable of driving one Schottky TTL load and 30 pF, or CMOS devices using external pullup resistors.

#### PORT 3 (P30-P37)

Port 3 can be configured as an I/O port, a bidirectional 8-bit data bus, or a multiplexed address/data bus depending on the operating mode. The TTL-compatible high-impedance output buffers can drive one Schottky TTL load and 90 pF. Unused lines can remain unconnected.

#### Port 3 In Single-Chip Mode

Port 3 is an 8-bit I/O port in the single-chip mode, with each line configured by the port 3 data direction register. There are also two lines,  $\overline{\text{IS3}}$  and  $\overline{\text{OS3}}$ , which can be used to control port 3 data transfers.

Three port 3 options are controlled by the port 3 control and status register and are available only in single-chip mode: (1) port 3 input data can be latched using  $\overline{\text{IS3}}$  as a control signal, (2)  $\overline{\text{OS3}}$  can be generated by either an MPU read or write to the port 3 data register, and (3) an  $\overline{\text{IRQ1}}$  interrupt can be enabled by an  $\overline{\text{IS3}}$  negative edge. Port 3 latch timing is shown in Figure 5.

|             | PORT                  | 3 CO | NTRO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | L ANI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | STA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TUS                                                                   | REGIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | TER                                                                                                                              |

|-------------|-----------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|